도시바 코퍼레이션(Toshiba Corporation)이 아날로그식 파워 반도체 애플리케이션용 정전기방전(ESD) 보호 디바이스를 개발했다. 이 디바이스는 첨단 0.13μm 프로세스 기술로 제작됐으며 트랜지스터 구조를 최적화하고 ESD 특성을 현저히 개선해준다.

ESD 보호 역량은 4배까지 증가해 훨씬 더 견고해졌으며 표준 편차는 기존 디바이스의 1/12밖에 되지 않는다. 도시바는 3D 시뮬레이션 분석을 통해 ESD 강도를 활성화하는 트랜지스터 구조 최적화 메커니즘을 파악했다. 도시바는 이런 내용을 2016년 6월 14일 체코에서 열린 국제 반도체 심포지엄인 “ISPSD2016"에서 발표했다.

ESD 전류 흐름이 실리콘 내부에서 국지적 온도를 상승시키기 때문에 인체 또는 장비로부터 ESD 서지를 투입하면 반도체 디바이스가 파괴될 수도 있다. ESD 보호 디바이스는 내부 회로를 보호해야 하는데 이는 특히 10V~100V까지의 높은 정격전압이 필요한 아날로그식 파워 반도체 디바이스의 경우에도 해당한다.

이 경우 ESD 보호 디바이스는 높은 전류 흐름을 확보해야 하는데 그 결과로 칩 사이즈가 증가하게 된다. ESD 보호 디바이스의 사이즈 축소는 더 콤팩트한 칩을 구현해야 하는 문제와 연결돼 있다.

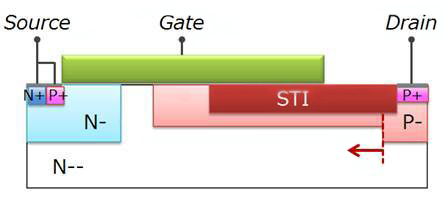

도시바는 ESD에 대한 3D 시뮬레이션 분석을 이용해 ESD 유도 파괴(ESD induced destruction)는 전기장 최고점에서의 전류 흐름으로 인한 격자 온도(lattice temperature) 상승 때문에 발생한다는 것을 밝혀냈다.

트랜지스터 구조를 변경해 드레인 저저항 영역을 소스 방향으로 확장하고 실리콘 측면 저항을 억제하면 전류 흐름이 드레인 바닥에서부터 소스 방향으로 전환되고 전기장 최고점에서 분리된다. 이렇게 최적화된 디자인은 ESD 강도를 4배까지 증가시키고 표준 편차는 1/12로 감소시킨다는 사실이 밝혀졌다. 또한 HBM*±2000V 확보를 필요로 하는 디바이스 사이즈가 68%로 줄어들었다.

도시바는 0.13μm 프로세스 기술의 첨단 아날로그 프로세스 플랫폼을 제공하는데 이 플랫폼은 저항기와 콘덴서 같은 수동 디바이스, CMOS, DMOS, 양극성 트랜지스터 등에 내장될 수 있다. 사용자는 다음의 세 가지 프로세스 플랫폼 중에서 각 애플리케이션에 적합한 프로세스를 선택할 수 있다.

주로 자동차에 사용되는 “BiCD-0.13”(최대 100V의 DMOS 라인업), 주로 모터 드라이버에 사용되는 “CD-0.13BL”(최대 60V의 DMOS 라인업), 주로 파워 관리 IC에 사용되는 “CD-0.13”(최대 40V의 DMOS 라인업).

도시바는 2017년에 이 기술이 적용된 CD-0.13 프로세스를 이용하는 제품을 출시하고 정전기방전 특성을 개선하기 위해 다른 프로세스 플랫폼을 계속 실행할 예정이다.